- Sony年度旗舰新机Xperia 1 V今日正式在台推出,今年4月上任以来首次参与中国台湾Xperia手机的上市发表的Sony Mobile中国台湾区总经理筒塩具隆 (Tomotaka Tsutsushio)表示,Xperia 1系列致力满足安卓高阶旗舰手机的市场需求,透过近年来集团内部的业务整合,Xperia 1系列历代的产品设计和技术创新持续在拍照、录像、游戏、音乐等领域带给消费者引领业界的全方位行动娱乐产品。Xperia 1 V采用Sony集团全新开发的双层式架构感光组件,同时整合Sony领先的相机

- 关键字:

安卓 SONY Xperia 1 V

- 年终的旗舰大乱斗还没有到来,但下半年以来的这几个月,各大手机厂商已纷纷推出了多款旗舰级产品,虽然索尼近年来在智能手机上表现不佳,但在旗舰产品上索尼仍不准备放弃。继此前全新的旗舰新品Xperia 5 Ⅱ的发布会官宣之后,现在有最新消息,近日知名爆料网站Slashleaks已经放出了该机的官方渲染图。据知名爆料网站Slashleaks最新发布的渲染图显示,与此前曝光的消息基本一致,全新的索尼Xperia 5 II自然是延续了Xperia系列标志性的外观设计风格,仍旧搭载了经典而富有标志性的 21:9“带鱼屏”

- 关键字:

索尼 Xperia

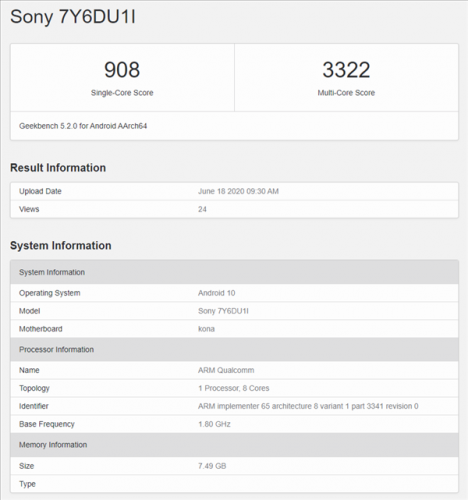

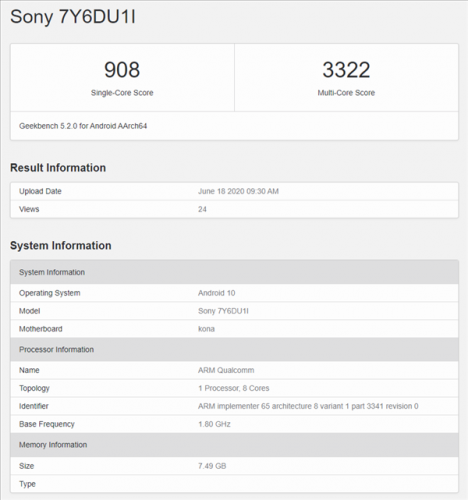

- 近日消息,型号为7Y6DU1I的索尼新机现身GeekBench跑分网站。如图所示,该机的单核成绩为908,多核成绩为3322,搭载高通骁龙865旗舰平台,配备8GB内存,运行Android 10。外媒猜测,这可能是索尼新一代旗舰Xperia 5 Ⅱ。之前索尼移动总裁Mitsuya Kishida在接受采访时透露,未来索尼移动旗舰将会沿用Ⅲ、Ⅳ这样的命名方式。由此看来,索尼Xperia 5的继任者将会命名为Xperia 5 Ⅱ。按照惯例,Xperia 5的继任者会在下半年登场,这款GeekBench网站刚刚

- 关键字:

Xperia 5 Ⅱ 索尼 骁龙865

- 索尼正式官宣了美版Xperia 1 Ⅱ的开售时间与价格,全球首款4K屏865机皇索尼Xperia 1 Ⅱ将于6月1日在美国开启预售,并于7月24日正式发货。 至于价格,只有8+256GB一个版本,售价1199.99美元,约合人民币8500元。 核心配置上,索尼Xperia 1 Ⅱ采用6.5英寸21:9 4K HDR OLED带鱼屏,分辨率为3840×1644,搭载高通骁龙865旗舰平台,配备8GB内存+256GB存储,前置800万像素,电池容量为4000mAh,支持IP68级防尘防水。 影像方面,索

- 关键字:

索尼 Xperia 1 Ⅱ

- 索尼Xperia 10 II已经开始在亚洲部分地区上市,虽然国行可能还需要等待一段时间,但港版、台版先行登陆。在中国香港市场,Xperia 10 II定价2599港币(约2390元人民币),在中国台湾市场,Xperia 10 II定价11490新台币(约2730元人民币),猜测国行版最终可能会定在2500元左右,颜色提供黑色、白色、绿色和蓝色。上市版本的固件是build 59.0.A.1.296,集成3月安全补丁,集成5月补丁的固件59.0.A.3.45也已开始陆续推送。和高端旗舰Xperia 1一样,索

- 关键字:

索尼 Xperia

- 据Phone Arena报道,索尼Xperia 1 Ⅱ在B&H开启预订,售价达到了1198美元(约合人民币8500元)。值得注意的是,预订之后不久B&H迅速删除了报价,并停止了预订,当前页面显示Xperia 1 Ⅱ即将推出,没有任何关于上市日期的信息。目前关于该机的国行版本售价没有确切信息,考虑到Xperia 1的国行首发价为6299元,Xperia 1 Ⅱ有可能会超过7000元,甚至不排除超过8000元的可能。该机最快会在6月份上市,值得期待。核心配置上,索尼Xperia 1 Ⅱ采用6.5英寸21:9

- 关键字:

索尼 Xperia 4K

- 索尼全新的 Xperia 10 II 更快将上架开卖,是延续了一贯的平实泛用的设计方向,为各位追求简单好用手机的朋友,带来 2020 年的新选择。因为继承了 21:9 电影银幕般的窄长比例和仅 151g 的重量,所以这台屏幕说是 6 寸之大的 Xperia 10 II,即使以单手持机也依然能灵巧操作。机身材质的改变,也让这台二代目在感觉上变得更高档 —— 由初代的仿金属色塑料机身,换上了康宁大猩猩 6 的机背玻璃,配合带防滑功能的雾面塑料中框,很是不错。说起机背,顺道也看看其设计,基本

- 关键字:

索尼 Xperia 10 II

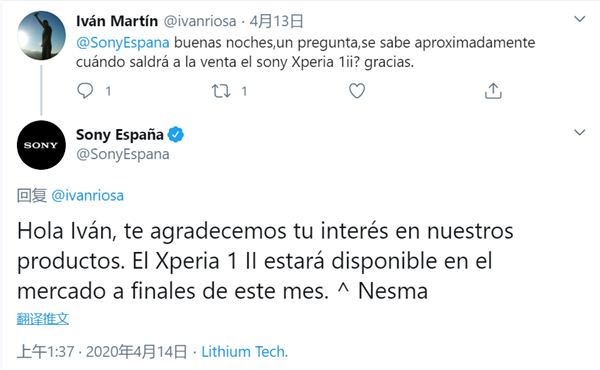

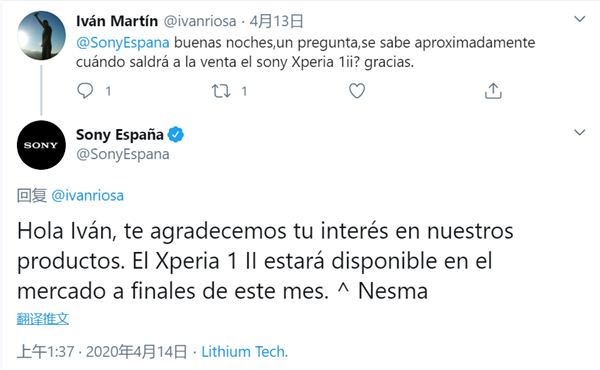

- 索尼西班牙官方推特在与网友互动时确认,Xperia 1 Ⅱ将在本月晚些时候上市,售价1200欧元(约合人民币9300元)。 核心配置上,索尼Xperia 1 Ⅱ采用6.5英寸21:9 4K HDR OLED带鱼屏,分辨率为3840×1644,搭载高通骁龙865旗舰平台,配备8GB内存+256GB存储,前置800万像素,电池容量为4000mAh,支持IP68级防尘防水。 影像方面,索尼Xperia 1 Ⅱ后置三颗1200万像素镜头,1200万主摄采用

- 关键字:

索尼 Xperia

- 在索尼今天的线上发布会前不久,原定于 MWC 上公布的新机也在最后一刻被彻底曝光。根据 XDA Devlopers 写手 Max Weinbach 的推文,索尼即将发布 Xperia 1 II 和 Xperia 10 II 这两款新品。其中 1 II 如其(怪怪的)名字所示,将会是去年旗舰 Xpeira 1 的升级版。它在保留 6.5 吋 4K HDR OLED 屏幕规格的同时,还能通过运动模糊降低技术达到「等同于 90Hz」的视觉效果。和真正的 90Hz 更新率面

- 关键字:

索尼、5G手机、Xperia 1

- 进入全面屏时候后,小屏手机生存空间愈发缩小。目前主流手机尺寸都在6寸或6寸以上,此前专为小屏用户打造的索尼Xperia Compact系列如今怎样了呢?IFA2019展会将于9月初亮相,按照惯例索尼将在本次展会上推出Xperia旗舰,可能还有传闻中的小屏手机Compact。8月6日消息,据Sumahoinfo报道,索尼有可能会在IFA2019展会上公布小屏手机Xperia Compact系列。值得注意的是,有人在XDA论坛上放出了HTML5测试截图,截图显示了一款Xperia新机型,型号为J9310,运行

- 关键字:

索尼 Xperia

- 索尼CEO平井一夫( Kazuo Hirai )本周五表示,公司会继续保留智能手机业务,尽管更强大的竞争对手统治了市场,未来,索尼仍然会成为竞争者。平井一夫在接受CNBC采访时表示:“在这一代智能手机中,我们不会指望自己能够成为第一名或者第二名,但是我们需要保留智能手机业务,保留个人通信业务,只有这样,当下一轮转变到来时,我们才有可能继续成为参与者,抓住机会,成为下一代通信设备的领导者。当然,希望索尼能够成为下一轮技术变革或者产品变革的发起者之一。”

最近索尼举行发布会,

- 关键字:

索尼 Xperia

- 今年9月正式亮相的Xperia Z5在外观上基本没有太多的变化,但非一体成型机身设计意味拆机更加容易,但事实上整个拆解过程并不轻松。首先在拆解过程中频繁使用到加热工序来移除胶水,甚至在几个元件的拆解中还需要使用撬棍来移除保护封盖,但非常有趣的是反而电池本身并不难拆卸。尽管设备元件替换非常容易,但是在此之前必须要移除所有的连接端口和移除粘性胶条。

在Xperia Z5中采用了标准的螺丝和粘合剂,尽管用户拆解中并不需要专用的工具但整个拆解相当的繁琐,需要很高的耐心才可以。

- 关键字:

Xperia Z5

- 10月8日据路透社称,索尼CEO平井一夫今日为旗下智能手机业务下达最后通牒,该公司将以下一财年作为衡量标准,若智能手机业务仍无法盈利,索尼将“为其考虑其它选择”。

众所周知,平井一夫多年来始终致力于索尼重组改革,回顾其改革之路不难发现,索尼近期业绩之所以出现稳步回升,其主要功绩在于平井一夫在大幅削减成本、剥离PC等疲软业务以及增强图像传感器及视频游戏销售方面的努力,相比之下,索尼在智能手机领域的进展却相当缓慢。

具体来说,根据索尼2014年公布的数据显示,包括Xpe

- 关键字:

索尼 Xperia

- 索尼的亏损梦魇依旧挥散不去:2014 财年,索尼的智慧型手机业务继续亏损,预计在截至 3 月的财年内,索尼净亏损会达到 2,300 亿日元(约合 19 亿美元 )。虽然近期索尼否认了“出售电视和手机业务”,但传言也从一个侧面说明了行动业务的不景气。

然而,索尼并不是在哪里都遭遇滑铁卢,在中东和非洲,索尼的销售情况依旧强劲。

据《华尔街日报》报导,索尼的手机产品在这两地的表现不错,索尼中东、非洲、土耳其的市场营销主管 Spyros Gousetis 表示,自推出 Xp

- 关键字:

索尼 Xperia Z

- 这个九月的手机界热闹不已,许多纷纷新机涌入市场。近日SONY 的新一代Xperia 系列旗舰机也开始发售了,SONY Xperia Z3 配置方面搭载高通骁龙(MSM8974AC) 2.5GHz四核处理器;配备一块5.2英寸,1600万色,1920x1080像素显示屏;电池容量约3100毫安,后置摄像头2070万像素;存储方面内存3GB RAM,闪存16GB,最高支持128GB扩展内存。

手机的外观和大致的性能前面已经熟悉过,不妨通过拆解,了解Z3的内部构造,半年一次的旗舰升级,除了外观变化,内

- 关键字:

e拆解 SONY Xperia

xperia 1 v介绍

您好,目前还没有人创建词条xperia 1 v!

欢迎您创建该词条,阐述对xperia 1 v的理解,并与今后在此搜索xperia 1 v的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473